SiriusHardware

Veteran Member

Thanks Dave - I haven't really had cause to read it because I don't actually own a PET to put it in but the executable has been extremely useful several times over for remote troubleshooting other people's poorly PETs.

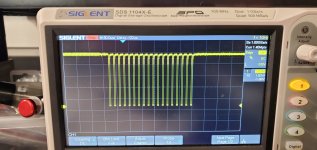

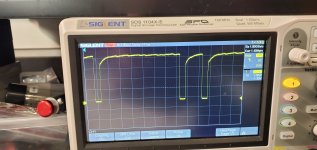

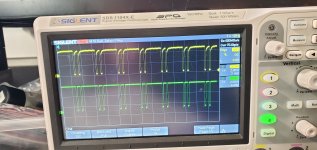

That's rather a lot of pulses to try to catch in the width of one screen and they will therefore be very narrow when captured that way. After we've counted how many _CS pulses Mike has captured, we may have to be content with only having the first five or so on screen so we can see what is happening to D0 (and ultimately the other data lines) during those pulses.

That's rather a lot of pulses to try to catch in the width of one screen and they will therefore be very narrow when captured that way. After we've counted how many _CS pulses Mike has captured, we may have to be content with only having the first five or so on screen so we can see what is happening to D0 (and ultimately the other data lines) during those pulses.